### Lattice Diamond の使い方 【LCMXO2-7000HE-B-EVN 基板を対象】

ver.2.12022/09/30

Y.T.

#### 1. 起動から書き込みまでの流れ

## 1)起動

Windows ∅ Start menu > Lattice Diamond x.xx(64-bit) > Lattice Diamond あるいは、プロジェクト名.lpf をダブルクリック

## 2) 新規プロジェクト作成の手順

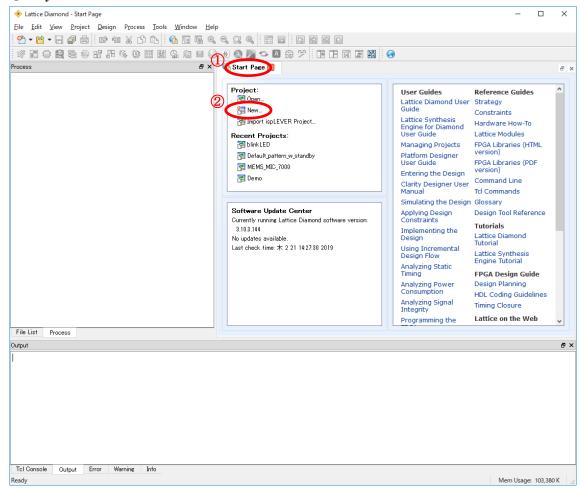

- ・ウィザードの開始

- ①Start Page から

- ②Project > New

◁

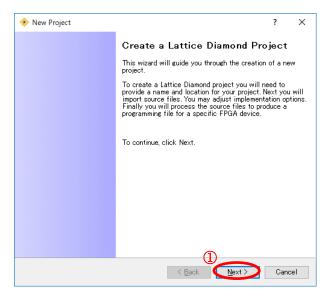

Dialog Box が開くので、①Next をクリックし、

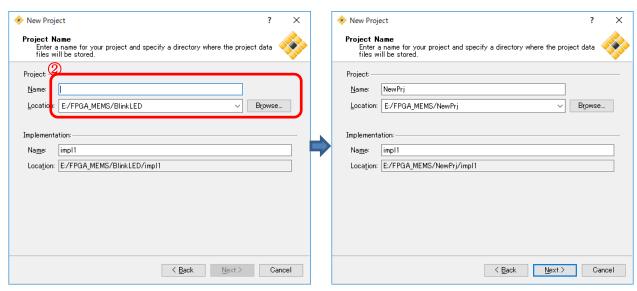

②Project 名を入力し、Browse…でディレクトリを指定

Implementation の表示で Location を確認。implement ファイル名を指定し Next

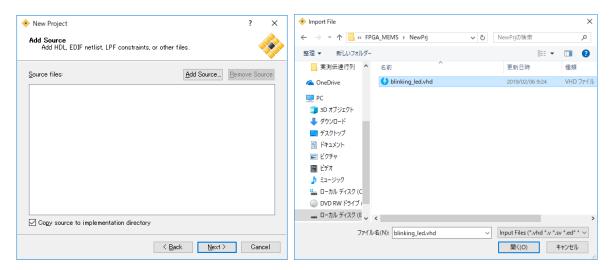

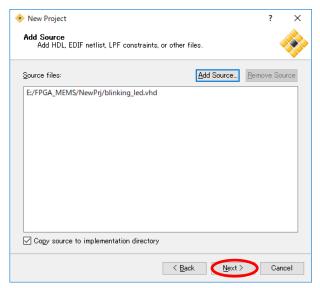

### ソースファイルの指定

①Add Source で source ファイル(VHDL コードなど)を指定

ソースコード(複数可)を追加し終わったら、Next クリック。

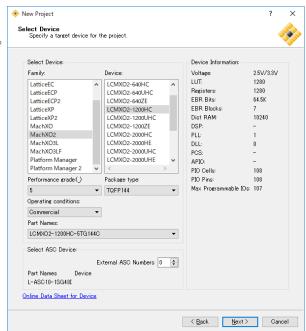

## デバイスの指定

Select Device ウインドウが開くので、デバイスを指定。 MachXO2 の場合,

MachXO2 > LCMXO2-7000HE

Performance Grade 4 を指定

Parts Names: LCMXO2-7000HE-4TG144I

と表示される

◁

Next をクリック

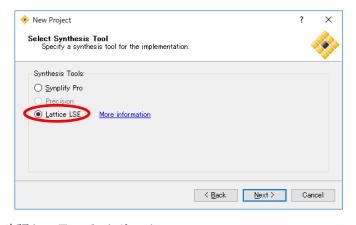

### ・合成ツールの選択

Select Synthesis Tool で Lattice ISE を指定し、Next をクリック

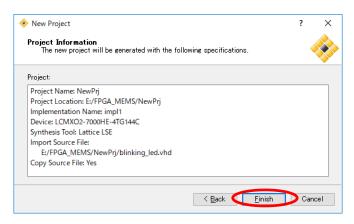

Project Information を確認し、Finish クリック。

以上で、新規プロジェクトの設定が終了。 指定したディレクトリの下に impl1 というディレクトリが作られる。

### 3)コンパイル(回路合成)

### •Export ファイルの指定

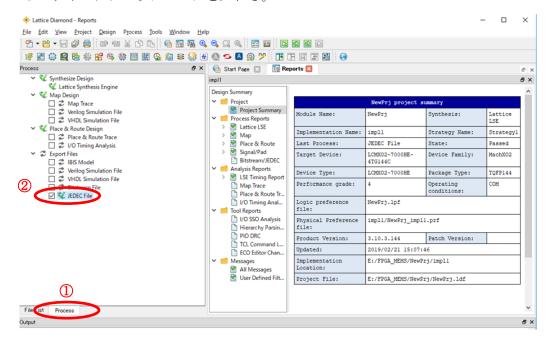

- ①ウインドウの Process タグを選択

- ②ツリーの下部, Export Files の中から出力したいファイルを選ぶ。シミュレーションをしない場合は, JEDEC ファイルにチェックマークを入れる。

ツリーに表示されている export したいファイル名をダブルクリックすると,合成のプロセスが進行し, 指定したファイル名のところに緑色のチェックマークが表示されれば,合成は終了。

# JEDEC File: FPGA 内部のハードウェア構成をプログラムするためのデータファイル。JEDEC は, Joint Electron Device Engineering Council (半導体技術協会) の略称。

## 4)Programmer の起動とデバイスへの書き込み

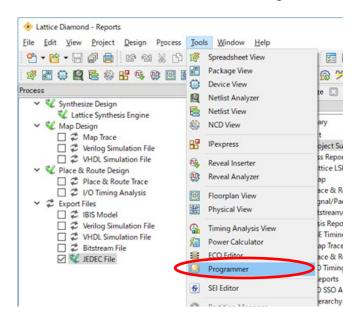

### •Programmer の起動

最上部のメニューバーから、Tools > Programmer により Programmer を起動

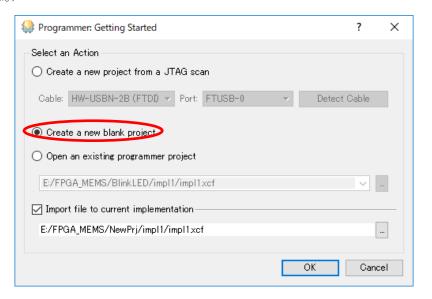

Programmer のウィザードが開始され、ダイアログボックスが表示される。Create a new blank project のラジオボタンを選択。(その上の JTAG scan から選ぶ ボタンを選択すると,正しいデバイスが設定 できないので注意。)

◁

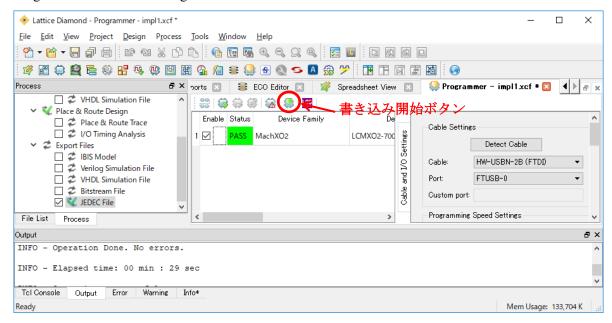

## ·デバイスへの書き込み

Programmer パネルから Program ボタンをクリックしてデバイスに書き込む

書き込みが終了次第デバイスは動作を開始するので、注意が必要。

## 2. ピンの割り当て

FPGAピンへの信号の割り当ての方法について説明する。VHDLなどのハードウェア記述言語(HDL) は、FPGA の論理構成をプログラムできる。しかし、HDL 自体には、対象とする FPGA のピンへの信 号の割り当てを記述する機能はなく、開発用ソフトが別途実行する。

## 1) Spreadsheet View を使うピン割り当て

Lattice Diamond でユーザがピン割り当てを指定する方法は複数存在する。以下では Spreadsheet View を使うピン割り当ての手順について解説する。

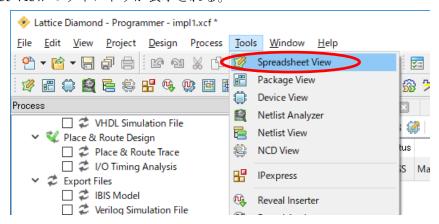

i ) Spreadsheet View を開く

メニューバー > Tools > Spreadsheet View

で Spreadsheet View のウインドウが表示される。

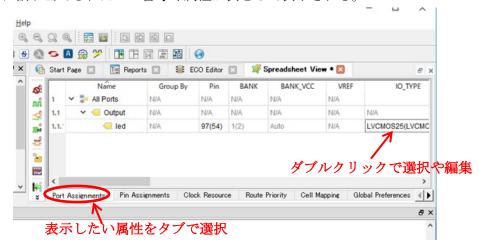

Spreadsheet View では設計データの様々な属性の表示や変更が可能になる。ピン割り当てに関連す る属性は、Port Assignments と Pin Assignments であり、ウインドウ下部のタブで選択できる。 ポートとそれに割り当てられたピン番号や属性が表として表示される。

#### **Port Assignments**

◁

VHDL コードで記述したトップレベルの回路の port が, Input, Output, Clock などに分類されて表示 される。特定の port に対して、割り当てるピン番号や属性を指定するために使う。デフォルトから変更 する可能性の高い属性としては、PULLMODEやIO TYPEがある。セルをダブルクリックすることで、 入力あるいは候補選択が可能

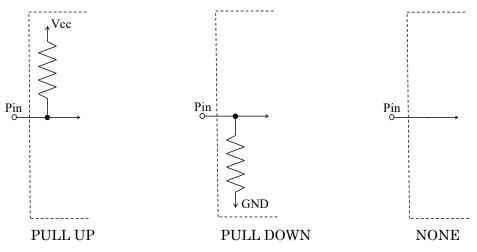

・PULL MODE: FPGA 内部で信号ピンを、抵抗を介して電源に接続する(プルアップ)か、グランド に接続する (プルダウン) かを指定する。 プルアップもプルダウンもせずに開放されている CMOS 論理 回路の入力は、論理レベルが不安定になるので、注意が必要。また、スイッチで論理信号を入力する場 合も、プルアップやプルダウンを指定することで、外付けの抵抗を略することができる。

PULL MODE の設定

・IO\_TYPE: 入出力の論理信号の規格を指定する。IO\_TYPE は接続する外部回路の規格に合わせる必要がある。(例えば LVCMOS25 は電源電圧 2.5V の CMOS 入出力規格である。) また、LED を駆動する場合は、明るく点灯させるため IO\_TYPE に LVCMOS33 を選択するなどのように、用途に合わせて選択する。

#### **Pin Assignments**

ピン番号を指定して、そのピンに割り当てる信号や属性を指定する際に使う。

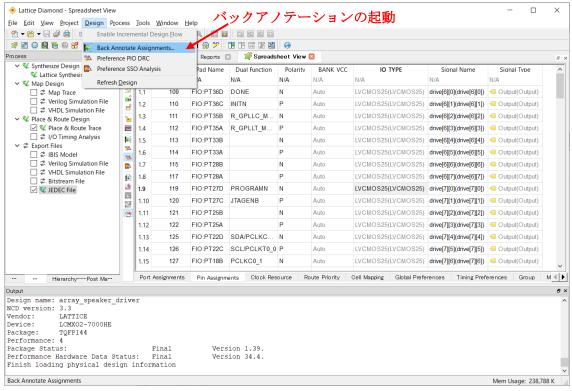

ii) バックアノテーション (Back Annotation)

バックアノテーションとは、ピン割り当てなどの回路レイアウトを変更した後に、それに合わせて回路の部品の接続情報(ネットリスト)を変更することである。

メニューバー > Design > Back Annotate Assignments...

によりバックアノテーションのプロセスを起動する。

起動すると、ダイアログボックスが開く。特別に指定することが無ければ、リターンキーを押すだけでよい。

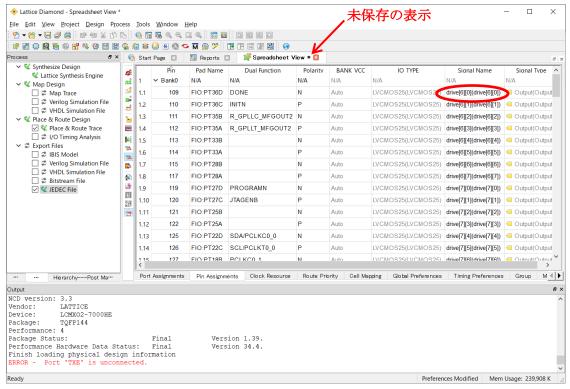

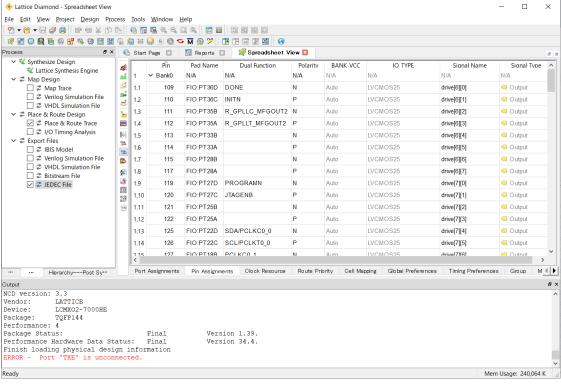

#### iii)Spread Sheet View の保存

◁

Spread Sheet View で、設定が保存されていない状態を図に示す。図の中の drive[6][0](drive[6][0]) のように、「ユーザが割り当てた属性(LatticeDiamond が割り当てた属性)」という表示になっている。 また、タブ名に" Spread Sheet View \*"のように、\*が表示されて未保存であることが表示されて いる。Spread Sheet タブ内で、Ctrl+s を押すことで、設定が保存される。同時に、属性名の括弧付き の記述も消える。

保存前の Spread Sheet View

保存後の Spread Sheet View

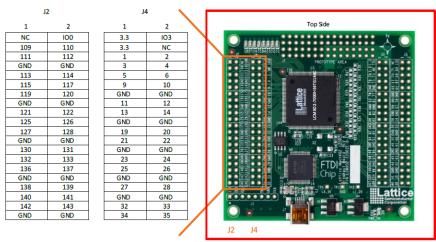

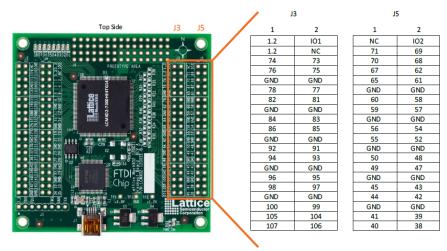

### 2)MachXO2 評価基板(LCMXO2-7000HE-B-EVN)でのピン割り当て

Lattice Diamond では、MachXO2 チップ本体の IO ピンに信号を割り当てる。MachXO2 を搭載した評価基板(LCMXO2-7000HE-B-EVN)を使う場合は、基板上に設けられた 4 組の 2×20 ヘッダピン用ランドを通して MachXO2 の IO ピンにアクセスすることになる。

# ランド (land): ピンをハンダ付けするため基板上に設けられた銅箔部分のこと

Figure 7.2. J3/J4 Header Landing Callout

Figure 7.3. J3/J5 Header Landing Callout

評価基板の外観とヘッダピンのランド

これらのヘッダピンと MachXO2 のピンでは、番号が異なり、対応関係も規則性が崩れている。

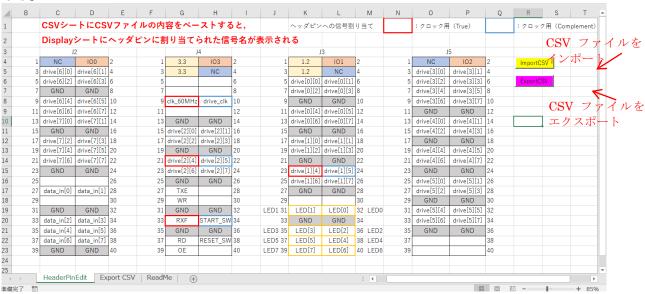

そこで、MachXO2のピンと評価基板のヘッダピンの対応関係の資料(例えば上の図)を確認しながら設計を進めることになる。この面倒な作業をサポートするため Excel ファイルを作成した。この Excel ファイル (MachXO2BB\_PinAssign.xlsm) を使ったヘッダピンへの信号割り当ての手順を以下に示す。

### ヘッダピンの信号割り当ての確認

i) CSV ファイルをエクスポート

Lattice Diamond で Spread Sheet View を開き, Pin Assignments タブを選びます。 メニューバーから

File > Export > Lattice CSV Files...

とすると、ファイル選択ダイアログボックスが開くので、フォルダとファイル名を指定してピン割り当て情報を表にした CSV ファイルを保存する

ii )MachXO2BB\_PinAssign.xlsm を起動し CSV ファイルをインポート

Excel のウインドウで HeaderPinEdit シートを選択し、シート右の上部にある"ImportCSV"と表 示されたボタンをクリックし、CSV ファイルをインポートする。HeaderPinEdit シートの表示が CSV ファイルのピン配置情報を反映したものに変化する。

なお、Latttice Diamond の Spread Sheet View からエクスポートした CSV ファイルを、 MachXO2BB\_PinAssign.xlsm の置かれたフォルダ内に配置しておくと,ファイル選択の操作が簡単に

HeadrPinEdit シート

#### ヘッダピンの信号割り当ての編集と CSV ファイルのエクスポート

i ) HeaderPinEdit シートのセルの文字列を編集して信号名の変更や並べ替えをする ただし、ユーザが希望した割り当てでは、Lattice Diamond での回路合成が不可能なこともある。ま た,ピンによっては割り当てた信号が機能しない事例も確認されている。さらに,クロック入力には専 用のピンがあるなど,注意が必要となる。

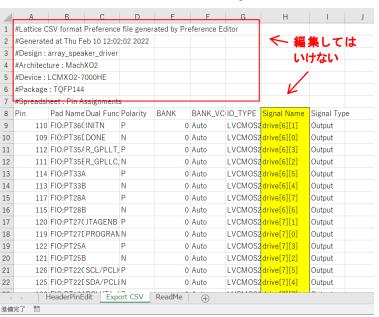

#### ii) Export CSV シートを編集

◁

Excel のウインドウで Export CSV シートに移動する。このシートは Lattice Diamond にエクスポート する CSV ファイルと一致している。現時点では,HeaderPinEdit シートで編集できるのは,信号の割り 当てのみなので, IO\_TYPE や SIGNAL TYPE などの属性は, Export CSV シートを編集して変更する。

**ExportCSV** シート

### iii) CSV ファイルをエクスポート

HeaderPinEdit シートに戻り, "ExportCSV" ボタンをクリックして, CSV ファイルをエクスポートする。

#### iv) Lattice Diamond で CSV ファイルをインポート

Spread Sheet View の Pin Assignments タブを選択した状態で,

メニューバー > File > Import > Lattice CSV File...

ダイアログボックスが開くので、インポートする CSV ファイルを選択する。

#### v ) Spread Sheet View で確認

ユーザが指定したピン割り当ては、設計の制約条件を満たさない可能性がある。Spread Sheet View でエラーが無いか確認し、バックアノテーションの操作をする。

### 3. プロジェクトの管理

Lattice Diamond では、設計(デザイン)をプロジェクトと呼ばれる単位で管理する。新規にプロジェクトを作成する方法は 1-2)「新規プロジェクト作成の手順」で説明した。以下では、既存プロジェクトのオープン、プロジェクトの複製、アーカイブ作成などの方法について解説する。

## 1) 既存のプロジェクトのオープン

方法 A: メニューバー > File > open > Project...

ダイアログボックスが開くので、プロジェクトファイル (×××.ldf) を選択

**方法 B**: Start Page タブで Open をクリック

ダイアログボックスが開くので、プロジェクトファイル (×××.ldf) を選択

**方法 C** : Start Page タブの Resent Project:のリストの中にあるプロジェクト名をクリック

既存のプロジェクトを開く際に使用する

#### 2)プロジェクトの複製

プロジェクトを複製する場合は、別名を付けてプロジェクトを保存すればよい。あるプロジェクトを 基に新しいプロジェクトを作成したり、テスト用の信号発生回路を組み込んだ回路を作成する際などに 複製を作成する。

メニューバー > File > Save Project As...

ダイアログボックスが開くので、保存先のフォルダとプロジェクト名を指定

#### 3)プロジェクトのアーカイブ作成

プロジェクトを他の PC で開発をしているメンバーにメールなどで送付する際に、圧縮されたアーカイブファイルを作成する。

メニューバー > File > Archive Project...

ダイアログボックスが開くので、保存先のフォルダとアーカイブのファイル名を指定する。アーカイブファイルは zip 形式になっている。なお、ダイアログボックスの Archive all files under the Project directory にチェックを入れておくと、プロジェクトフォルダ内のすべてのフォルダとファイルがアーカイブされる。チェックを外した状態では、プロジェクトに関連するフォルダとファイルのみがアーカイブされる。

#### ・アーカイブファイルからのプロジェクトの復元

メニューバー > File > Open > Archived Project...

を使う。

zip 形式のアーカイブを解凍するだけではプロジェクトを復元できないことがあるので注意。

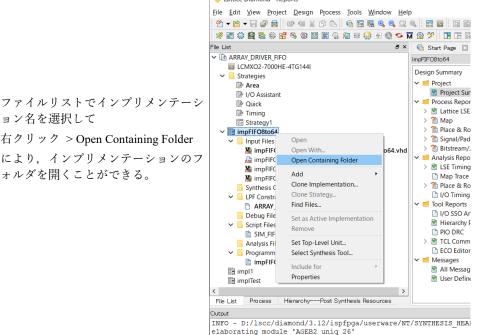

## 4)複数のインプリメンテーションの管理

インプリメンテーション(Implementation)とは、一般には"**実装**"と和訳されている用語である。設計データを基に、実際に動くハードウェアやソフトウェアを作ることを指す。Lattice Diamond では、インプリメンテーションとは「ソースファイルやモジュール、あるいはオプション設定や各設計制約の組み合わせの呼称」のことである。

Lattice Diamond ではデフォルトで"imp1"という名称のインプリメンテーションが生成される。

ョン名を選択して 右クリック > Open Containing Folder により、インプリメンテーションのフ

ォルダを開くことができる。

インプリメンテーションフォルダを開く

1つのプロジェクトは複数のインプリメンテーションを持つことができる。VHDL コードや、速度・ 回路面積の優先度の変更など、条件を変えて検討することが可能になる。

- i) インプリメンテーションの新規作成または、クローンの作成

- •新規作成

◁

メニューバー > File > New > Implementation...

ダイアログボックスが開く → 名前などを入力

クローンの作成

File List で元となるインプリメンテーション (impl など) を選択し,

右クリック > Clone Implementation...

ダイアログボックスで, Copy files into new implementation source directory を選択すると,

source フォルダに元のソースコードがコピーされる

ii) アクティブなインプリメンテーションの選択

アクティブにするインプリメンテーションを選択

右クリック > Set as Active Implementation

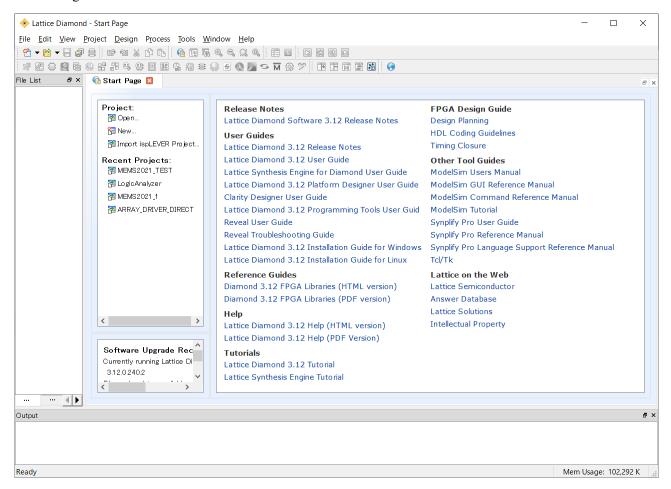

# 4. その他

Start Page には、ユーザガイドなどへのリンクが配置されている。

#### 5. IPExpress の使い方

IP (Interectual Property) とは、一般には、特許権や著作権などの知的財産権を表す用語である。 半導体業界では、IP とは LSI の設計データを機能単位でまとめたものを指し、「形の無い商品」として 提供されている。"マクロ"とも呼ばれている。IPを使うことで、ユーザが HDL を使って設計するよ り、回路面積や動作速度の点で優れた機能ブロックを実現できる。

IPは、半導体製造用マスクパターンとして提供されるハードマクロと、RTL やネットリストの形で 提供されるソフトマクロに分類できる。

Lattice Diamond でも、IPExpress というツールを使うことで、IO やメモリなど様々な IP が無償で 使えるようになっている。以下では、FIFO を構築する例を使って、IPExpress の使い方を解説する。

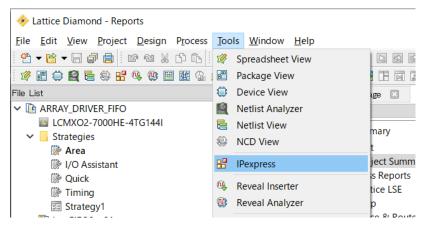

## 1) IPExpress の起動

メニューバー > Tools > IPExpress

IPEXpress の起動

デフォルトの設定では、Lattice Diamond のウインドウに IPExpress のタブが追加される。

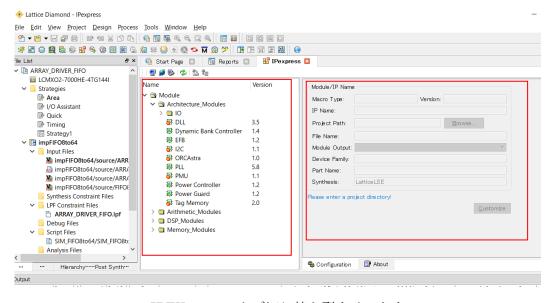

IPEXpress のタブ切り替え型ウインドウ

#### 2)モジュール/IP の作成

IPExpress タブウインドウは、左枠にモジュール名のツリーが、右枠にツリーで選択されたモジュー ルのパラメータを設定する部分に分かれている。

i) 生成するモジュールを選択し、パラメータを入力

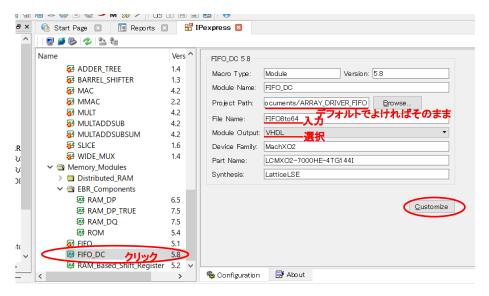

モジュール名のツリーから、目的とするモジュールを選びクリックする。(例として、FIFO\_DCを選 択)

◁

モジュール名をクリック

右枠でモジュールのパラメータを設定する。ユーザは以下の項目を設定する。

・Priject Path: デフォルト設定でよければ、そのままにする

・File Name: 生成したモジュールを保存するファイル名

・Module Output: VHDL か Verilog かを選択(例では VHDL を選択)

必要なパラメータが設定されると、右下にある"Customize"ボタンがアクティブになる。

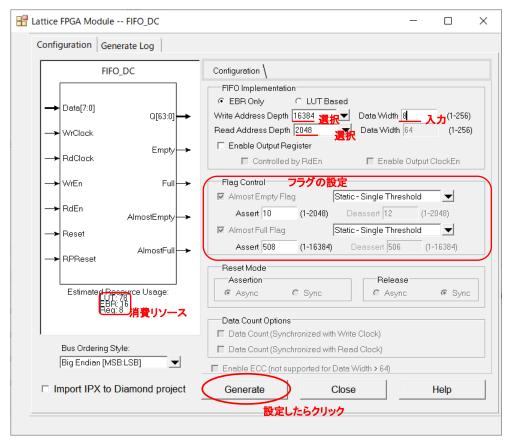

### iii) モジュールのカスタマイズ

"Customize" ボタンをクリックすることで、カスタマイズ用の別ウインドウが開く。

モジュールのカスタマイズ

設定パラメータは,生成するモジュールごとに異なる。例に挙げた FIFO\_DS モジュールでは,以下 の項目を設定している。

- ・Write-Address Depth:入力側から見た FIFO の深さを選択

- ・Data Width: FIFO 入力のデータ幅を入力

- ・Read-Address Depth: 出力側から見た FIFO の深さ 以上の3項目を選択すると、出力側のデータ幅 Data Width は自動的に定まる。

- Flag Contorol: FIFO の状態をモニタするフラグが 1 になる条件を設定 Almost Empty Flag: "FIFO がほとんど空"を示す。1 になる閾値を Assert 欄で設定 Almost Fill Flag: "FIFO がほとんどフル"を示す。1 になる閾値を Assert 欄で設定

なお、フラグの設定モードはデフォルトの Static-Single Threshold を選択している場合、閾値は、 IPExpress で設定した際の値に固定される。Dynamic-Single Threshold に変更すると, FIFO に閾値設 定用の入力ポートが生成され外部から制御できるようになる。

- ・Import IPX to Diamond Project: チェックを入れると、IPExpress で設定できる全てのパラメータ を含んだ設計データが、プロジェクトに取り込まれる。これにより、後で設定しなおすことが可能にな る。

- iv) モジュールの生成

カスタマイズの操作が完了したら、"Generate ボタン"をクリックすると、モジュールに関連するフ ァイルが生成される。モジュールの HDL コードは、プロジェクトフォルダ内に配置されるので、これ をプロジェクトに取り込む操作は、ユーザが手動で実行する。