評価基板

現在,MEMSマイクアレイ用データ収集システムは,Mach XO2評価基板(MachXO2 Breakout Board Evaluation Kit)を使っています。その際,評価基板のFPGAの入力ピンの一部がプルアップされている仕様に気付かなかったため結構な時間を費やしてしまいました。この投稿では,そのトラブルと評価基板のピンに関する注意点について整理します。

動作チェックまでの手順のおさらい

動作チェックまでの手順をおさらいしておきます。

ハードウェアの構築(Lattice Diamondを使用)

- VHDLコードを入力・編集

- JEDECファイルを作成

- ピン割り当て

Spreadsheet ViewのPin AssignmentsタブからFile > Export > Lattice CSVファイル によりピン配置のCSVファイルをエクスポートする。これをピン配置用のExcelファイルで読込み編集してからCSVファイルを出力し,Spreadsheet ViewでインポートしてLattice Diamondのプロジェクトに取り込む。 - IO属性の設定

Spreadsheet ViewのPort Assignmentsタブを開き,入出力ピンのPull Up/Pull Downの設定などをする。デフォルトの設定では入力ピンは全てPull Downになっている。タクトスイッチによるリセット用と動作開始用の入力ピン(VHDLコードでの信号名はRESET_SWとSTART_SW)はPull Upに指定する。なお,Pull Down,Pull Upともに抵抗値は公証で10kΩとなっている。 - 書き込み(Program)

動作チェック

- テスト信号の設定

確認したい内容に合わせてテスト用入力信号を設定する。例えば,チャンネル0のビット0に対応するマイク入力ピン(信号名mic_in[0][0])をVddに接続する。これによりチャンネル0の信号は常に“1”(0000 0001)というデータとして受信されるはず。 - テスト用C++コードでデータ受信

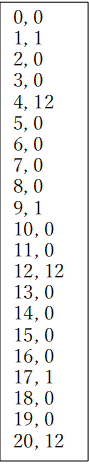

上記の設定で受信したデータを10進数で表示すると,以下のようなデータが受信されています。左側の欄が受信データの番号,右側が受信データです。

冒頭(受信番号0)で“0”が受信されています。おそらく,書込まれたものではなく出力レジスタの初期データと考えられます。次に受信される番号1の“1”がテスト用信号として設定したチャンネル0の値と考えられます。この3つ後ろの4番目のデータはチャンネル3のデータです。設定では入力ピンはプルダウンになっているので“0”となるはずですが,“12”(2進数では0000 1100)となっています。さらに,ここに示したデータでは,“1”と“12”は周期8で出現していきますが,ときどき周期がずれることがわかりました。どこかでデータが欠落したり逆に追加されたりしている可能性があります。

また,卒研の学生さんが使っているピン割り当てが異なる別の基板では,チャンネル3以外のところに“96”(1100 0000)という値が現れています。これらのことから,以下のような問題があることがわかります。

- 受信されたデータに設定していない値が現れる

- 受信データの周期が8からずれることがある

この時点で設定していない値が特定の2つの入力ピンと関連していることに気付いていれば,評価基板のユーザガイドを見直したはずです。しかし,

- 構築したハードウェアの問題ではないか

例えば,データ転送のロジック回路の設計に問題がある。論理シミュレーションでは問題なく動いているので,実装した際の回路の問題,例えば論理回路のハザードやジッタ,グラウンドバウンスの影響かもしれない。FPGAとUSB転送インタフェースFT232Hをジャンパワイヤで接続しているため雑音に弱いので,そのせいか? - USB転送の仕様の問題

何かイベントコードを追加しているのではないか?

などと,いろいろ考えて設計の見直しやテストを繰り返しました。64ビット入力8ビット出力のFIFOを使う,よりシンプルなハードウェアにしても同じ問題が起きた段階で,やっと気が付きました。

2つの信号ピンが外部でプルアップされていた

以下はMach XO2評価基板のユーザガイドに載っている基板の回路図です。中ほどに配置されたU3-2と表記されているICがMach XO2 FPGAです。注目していただきたいのは,125番と126番の2つのピンが2.2kΩの抵抗でプルアップされていることです。

この2つのピンは汎用の信号ピンまたはI2Cインタフェース用の信号ピン専用に設定することができます。そして,125番ピンはI2CのSDA,126番ピンはI2CのSCLとして使うように基板上で2.2kΩの抵抗で電源Vddにプルアップされていました。

2つのピンは開発中のシステムではmic_in[3][3]とmic_in[3][2],つまりチャンネル3のビット3と2に対応しています。Lattice Diamondのピン割り当てでは,FPGA内部で公称値10kΩでプルダウンする設定になっていても,外部で2.2kΩでプルアップされていては,ピンに何も接続していない場合は“1”が入力されることになります。

これが,チャンネル3のデータが“12”になった原因です。そこで,入力ピンmic_in[3][3]とmic_in[3][2]をGNDに接続すると,“12”ではなく“0”が受信されるようになり,このことが確認できました。

評価基板の設定で注意すべきこと

評価基板に搭載されてるFPGAのピンは,ユーザが自由に使えないものもあることはユーザガイドで把握していました。しかし2つのピンが基板上でプルアップされていたことは,ユーザガイドの末尾に載っていた回路図を見直すまで気が付きませんでした。

その他の評価基板でのピン割り当てについての注意点も併せて挙げておきます。

- ヘッダJ2の19番,20番はI2C用に抵抗2.2kΩでプルアップされている

プルアップされていることに留意すれば,汎用の入出力として使うことは可能と考えられます。 - ヘッダJ2の25,26,29,30番はFPGAのJTAGプログラム専用に使われている

この4つのピンは,Lattice Diamonndで設定できても,使うことはできません。 - ヘッダJ3の31,32,35~40番ピンは基板上のLEDに接続されている

汎用の入出力として使うことは可能と思われます。しかし,高速に変化する信号を扱う場合は,LEDが負荷になるので動的な特性が他のピンと異なってくる可能性があります。

以上のピンについては,ピン割り当て用のExcelファイルでは色分けなどにより注意できるようにしています。(ヘッダJ2の19番,20番については今後,反映させる予定)

なお,Lattice Diamondのピン割り当ては(当然ながら)評価基板上の接続やピンの役割の情報は反映されていません。FPGA内部だけでなく,基板上,さらに基板外の周辺回路との接続状況を読み取る仕組みについて卒業研究のテーマとして,概念設計まではしたことがあります。

残された問題

今回の「データ化け」の問題は,回路図の見落としという,恥ずかしい原因で起きました。開発や工作で出会うトラブルのほとんどは,思い込みで発生します。今回も「開発ソフトで,プルダウン設定にしたから大丈夫」という勝手な思い込みが原因となって,少なくない時間を消費してしまいました。

一方,受信データの周期がずれる問題は残っています。この「フレームずれ」の問題は,送信データに同期用の信号を追加することで対応することにしました。既にハードウェア構成を変更して動作も確認したので,別稿で報告することにします。また,論理回路のハザードやジッタ,雑音が影響としていると考えられる不安定な挙動も見られますので,今後,原因を詰めて対策を考えていく予定です。

コメント